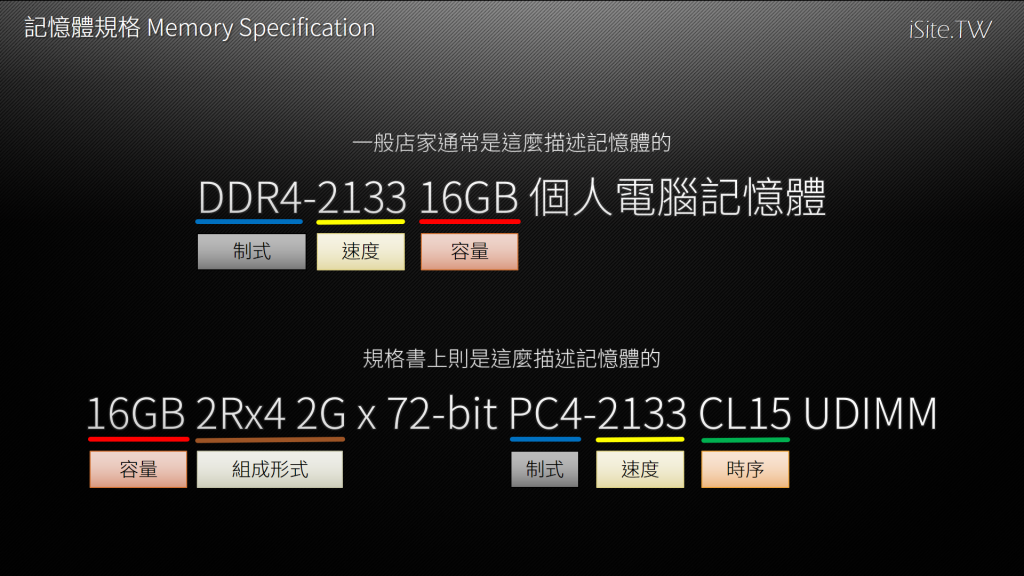

延續上一篇介紹記憶體規格,這篇我們同樣從上節出現過的這張圖開始進行,討論完記憶體制式與速度與頻寬的問題之後,我接下來想介紹的是記憶體時序的部分,下篇則會談記憶體的特殊功能與組成形式的部分,作為記憶體規格介紹的尾聲。

記憶體時序的意義

如果不出意外的話,記憶體時序 (Timing) 會是所有記憶體規格參數中最複雜且最難理解的部分,顧名思義記憶體時序與時間有關,什麼樣的時間呢?其實就是記憶體進行各類操作 (例如收到處理器要求後要讀取資料中間的過程) 時所需要花費的時間 (單位是需要經過幾個時脈週期,所以時脈提升也會影響到時序,所以不見得只要時序越低就一定越好,要算過才知道),時序規格通常是由如下圖中的四組數字組成,依序分別是 CL、tRCD、tRP 與 tRAS。

話說從頭-記憶體存取資料的方式

要解釋時序的意義之前,我們需要先理解記憶體是如何存放與讀取資料的,基本上我們可以將記憶體想像成一個很大的矩陣,由大量的欄位組成 (欄位的數量就是記憶體的容量) 每個欄位都有一個專屬的位置 (X,Y),以下圖的例子而言,資料放在 (3,4) 這個欄位中。

當處理器發出指令要求存取 (3,4) 欄位的資料後,記憶體會將指令的內容解碼,得到要存取的列位置為 X = 3,欄位置 Y = 4,之後記憶體會啟動整個第三列的所有欄位以備存取。

接下來記憶體會使用指令解碼之後得到的欄編號來指出要存取的欄位位置並進行存取。

之後如果要存取的下一個資料也在同一列的話,就不需要重新執行 Step 2 了,直接把欄位編號指標移到要存取的欄位就可以了。

如果接下來要存取的資料不是放在同一列的話,則會需要將之前啟動的那一列關掉,之後再重做一次 Step 2 做過的事情,將資料所在列的所有欄位啟動。

Table of Contents

回到時序本身

看完記憶體存取資料的方式與過程之後,我們現在就可以回頭談時序本身了,如同本節一開始出現過的這張圖,時序通常由四組數字組成:

首先從意義比較簡單的 tRAS 開始,RAS 的全名是 Row Address Strobe,也就是列位置閘門切換的延遲時間,其實就是前面記憶體存取步驟中說明過的「啟動一整列」所需要的時脈週期數。

另一個時序參數則是 tRCD,RCD 的全名是 RAS to CAS Delay,也就是記憶體完成啟動一整列之後,到開始選定欄之前這中間經過的延遲時間。

第三個時序參數則是 tRP,RP 的全名是 RAS Precharge,意義上則是前面介紹記憶體存取步驟中的 Step 5 內,要將原本已經啟動的一整列關閉,再到開始啟動另一列這之間所經過的時脈週期數。

最後要談的時序參數 (同時也是一般來說我們比較在意的) 就是上圖顯示的第一組數字,CL 的全名是 CAS (Column Address Strobe) Latency,也就是前面提過的,如果要存取的資料都在同一列的狀況下,就不需要重新啟動其他列,而可以直接存取同列的另一個欄位,也就是欄位編號定位之後到真正取得資料這之間所經過的時脈週期數。

時序越高,延遲就一定越高嗎?

這個問題大概是不少人都會有的疑問,因為從前面的說明看起來好像時序高是一件很不好的事情?但實際上並不這麼單純,要特別留意到時序的單位並不是秒,而是時脈週期 (clock cycle) 數,所以會跟記憶體的運作時脈有直接關係,所以這個問題的答案是否定的。

以時序 15 的 DDR4-2400 來說好了,運作時脈為 300 MHz,每個時脈週期換算成時間其實是 3.33ns (nanoseconds),因此 15 個時序經過的延遲時間是 49.95 ns,如果我們拿一個時序 14 的 DDR4-2133 來對比,由於運作時脈下降到 266 MHz,每個時脈週期換算的時間就增加到 3.76 ns,經過 14 個時序其實會有 52.64 ns 的延遲,這就是一個時序低但其實延遲反而長的例子,基本上在高時脈記憶體上看到較高的時序這也是其中一個原因。

近來風氣強調時脈多於時序

其實時至今日已經很少聽到有人特別在意時序的問題了,也越來越少聽說有人要「特挑低時序」的記憶體模組,甚至連超頻玩家也漸漸較少人去研究時序的調校,或許是因為時脈提升帶來的性能提升遠較時序降低來得明顯,而降低時序的困難度卻比拉高時脈來得困難許多的緣故吧?

當然如果要追求效能的最大極限,選擇時脈最高「且」同時有最低時序的組合應該是可以帶來最佳效果的,但付出如此多時間心力換來的效果是否明顯到值得這麼做,恐怕就有待商榷了。