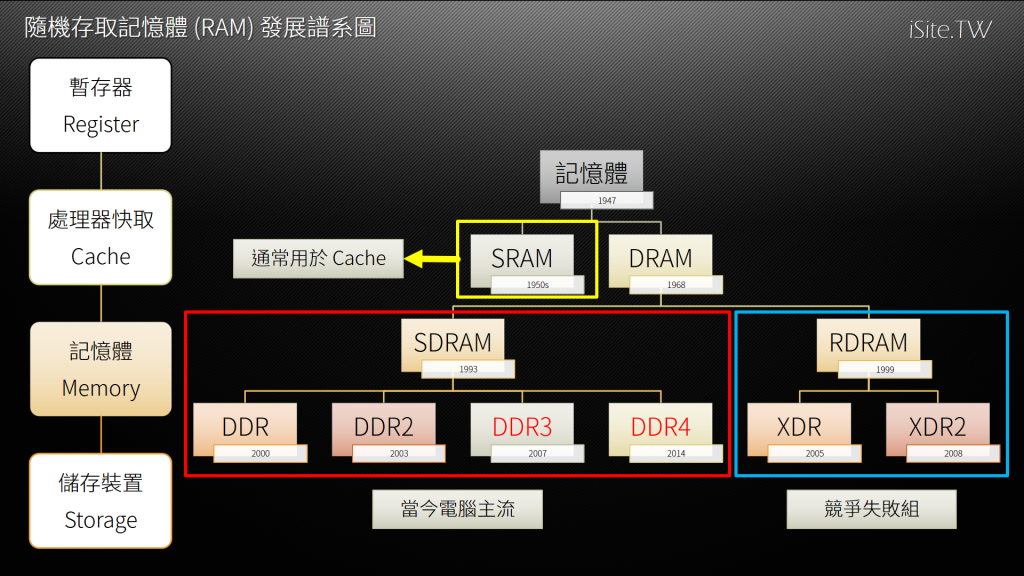

介紹完記憶體的規格之後,接下來的主題將是近二十年內個人電腦主要使用的記憶體的歷代發展,一切依然要回到之前就使用過的這張譜系圖:

Table of Contents

DRAM 與 SRAM

DRAM 的全名是 Dynamic Random Access Memory (動態隨機存取記憶體),其實命名上正好是相對 SRAM 的 Static Random Access Memory (靜態隨機存取記憶體) 而來,這兩種都是具揮發性的記憶體,原理上也大致相同 (運用通電與否來決定資料是 0 或 1),主要的差異在於實作的方法不同,SRAM 的結構主要為 flip-flop 正反器,而 DRAM 則是使用電容器搭配電晶體的組合來達成相同的目的,這兩種不同的實作方式也導致最後兩種記憶體產生了截然不同的特色:

- DRAM 需要週期性的更新 (Refresh),也就是重新對電容器充電,否則資料會消失,而 SRAM 則不會 (其實這就是命名中 Dynamic 與 Static 的由來),但 SRAM 在完全斷電後資料也會消失,因此仍然是具揮發性記憶體的一種。

- DRAM 的構造比較簡單,SRAM 則相對而言複雜了許多。

- 由於 SRAM 結構複雜,所以成本也比 DRAM 高了很多。

- 由於 DRAM 結構簡單,所以要做出大容量的 DRAM 遠比 SRAM 容易。

- 因此最後 DRAM 成為電腦記憶體的主流,SRAM 則主要只用於快取的部分。

SDRAM

活躍年代:1996 ~ 2001

針腳配置:168 針

封裝方式:TSOP

工作電壓:3.3 V

單條模組最大容量:1 GB (UDIMM)、2 GB (RDIMM)

單一顆粒晶片 Bank 數量:1 或 2 或 4

同步動態隨機存取記憶體 (Synchronous Dynamic Random Access Memory, SDRAM) 是 DRAM 的其中一種,在近二十年之內在個人電腦領域獲得極為廣泛的運用 (在 SDRAM 之前個人電腦還使用過 EDO、FPM 等老式 DRAM,不過由於年代久遠所以這裡就不談了),迄今最新的個人電腦與伺服器也仍然是使用由 SDRAM 改進而來的記憶體。

SDRAM 與其他種類的 DRAM 最大的不同就在於「同步」,這裡的同步指的是透過在記憶體上實作同步時脈產生器,使記憶體與處理器的運作時脈一致 (也就是後來我們所知道的「外頻」的概念),這樣做的好處在於從此記憶體的頻率可以獲得很大的提升 (超過 100 MHz 以上的記憶體運作時脈成為可能),而且透過與處理器同步時脈,記憶體可以更精準的在處理器需要資料時就降資料送出,讓處理器不必耗費多餘的時間在等待記憶體的下一個時脈週期上。

SDRAM 時期的記憶體模組根據顆粒晶片的分布方式,可分為單面與雙面模組,由於記憶體顆粒晶片的技術提升使得單顆顆粒晶片可以裝載的資料量增加,因此同樣容量的記憶體模組可能同時有單面與雙面版本流通於市面上,這在某些主機板上會出現一些問題 (例如只認得到一半容量),所以當時採購記憶體要考慮的事情其實還蠻複雜的。

由於後來發展的 DDR 記憶體為雙倍資料傳輸率,因此僅有單倍資料傳輸速率能力的 SDRAM 後來也被稱為 SDR (Single Data Rate) SDRAM。

| 規格 | 制式 | 運作時脈 | 每秒資料傳輸率 |

| PC66 (主流) | SDRAM | 66 MHz | 528 MB/s |

| PC100 (主流) | SDRAM | 100 MHz | 800 MB/s |

| PC133 | SDRAM | 133 MHz | 1064 MB/s |

DDR SDRAM

活躍年代:2001 ~ 2005

針腳配置:184 針

封裝方式:TSOP 與 BGA 兼有

工作電壓:3.3 V

單條模組最大容量:1 GB (UDIMM)、2 GB (RDIMM)

單一顆粒晶片 Bank 數量:4

DDR 是 Double Data Rate 的縮寫,也就是雙倍資料傳輸率的意思,與原本的 SDRAM 最大的差別在於本來 SDRAM 只有在時脈振幅要往高點走的時候才能進行資料傳輸,而 DDR SDRAM 由於運用了大小為 2n (足足是 SDRAM 的兩倍) 的預取技術 (Prefetch,在存取資料的時候,除了要求的資料本身外,順便將其他資料也放進 I/O 緩衝區中一次發出),在時脈振幅將往高點或低點的時候都可以各進行一次傳輸 (也就是一個時脈周期內可以有兩次資料傳輸,這項技術稱為 Double Transition),所以單位時間內的資料傳輸率就是前代的兩倍了。

然後到這裡就會衍伸出另一個問題了,剛剛才說 SDRAM 讓記憶體時脈可以輕易大幅拉高,那為什麼還要發展 DDR SDRAM 而不是單純繼續把 SDRAM 的時脈拉高就好呢?

實際上就是廠商又再次碰壁了 (還記得之前我說過 DRAM 要保存資料要靠持續、定期地對電容器充電嗎?充電速度也不可能永無止盡的提升),提升到 166 MHz 之後廠商就發現已經很難再將記憶體的時脈往上拉,所以時至今日就算是 DDR4 SDRAM,其實內部時脈最高也都僅到 300 MHz 附近而已。

除此之外,如同過去 SDRAM 一般,為了讓單一記憶體模組的容量能夠有效提高,DDR SDRAM 也會使用分組的方式來在單一記憶體模組上面放上更多的記憶體顆粒晶片,但不同於 SDRAM 時期以單、雙面 (Double Side 或 Single Side) 做區分,從 DDR SDRAM 開始我們將記憶體顆粒晶片的分組稱為 Rank ,至於原因呢,就如同上一節談過的,單面有可能不只一個 Rank,雙面也有可能只有一個 Rank,Rank 的數量要視乎實際顆粒晶片之間拉線的方式而定,而不一定與外觀相符。

| 規格 | 制式 | 運作時脈 | 每秒資料傳輸率 |

| DDR-200 (少見) | DDR | 100 MHz | 1600 MB/s |

| DDR-266 (主流) | DDR | 133 MHz | 2133 MB/s |

| DDR-333 (主流) | DDR | 166 MHz | 2666 MB/s |

| DDR-400 (主流) | DDR | 200 MHz | 3200 MB/s |

DDR2 SDRAM

活躍年代:2004 ~ 2009

針腳配置:240 針

封裝方式:BGA

工作電壓:1.8 V

單條模組最大容量:4 GB (UDIMM)、8 GB (RDIMM、FB-DIMM)

單一顆粒晶片 Bank 數量:4 或 8

DDR2 顧名思義是第二代的 DDR 記憶體,絕大多數的功能都與 DDR SDRAM 差不多,最明顯的差異在於 DDR2 SDRAM 的預取資料量是 DDR SDRAM 了兩倍 (由 2n 升級為 4n),所以 DDR2 SDRAM 的 I/O 運作時脈比 DDR SDRAM 又再次提高了一倍,這連帶也就造就了在同樣運作時脈下,DDR2 SDRAM 的每秒資料傳輸率可以再次加倍的效果。

從 DDR2 SDRAM 開始,記憶體顆粒晶片則必須使用成本較高的 BGA 封裝 (以往的 TSOP 封裝沒辦法滿足 DDR2 SDRAM 在高速下維持訊號完整與針腳數增加的需求,且 TSOP 外露且向外延伸的針腳在時脈拉高之後會產生嚴重的寄生電容與電阻拉高的現象),使用 BGA 封裝的另一個好處是 BGA 晶片的體積比起 TSOP 封裝來得小上許多,讓記憶體模組上有更多空間可以堆疊記憶體顆粒了,這也是為了推出更大容量的記憶體模組所必須具備的特性。

除此之外,受益於製造工藝的提升,DDR2 SDRAM 的工作電壓比起前代來說大幅降低為 1.8 V。

| 規格 | 制式 | 運作時脈 | 每秒資料傳輸率 |

| DDR2-400 (少見) | DDR2 | 100 MHz | 3200 MB/s |

| DDR2-533 | DDR2 | 133 MHz | 4266 MB/s |

| DDR2-667 (主流) | DDR2 | 166 MHz | 5333 MB/s |

| DDR2-800 (主流) | DDR2 | 200 MHz | 6400 MB/s |

| DDR2-1066 (少見) | DDR2 | 266 MHz | 8533 MB/s |

DDR3 SDRAM

活躍年代:2007 年至今

針腳配置:240 針

封裝方式:BGA

工作電壓:1.5 V (DDR3)、1.35 V (DDR3L)

單條模組最大容量:8 GB (UDIMM)、16 GB (RDIMM)

單一顆粒晶片 Bank 數量:8

DDR3 SDRAM 應該是目前絕大多數人正在使用的記憶體吧?做為第三代的雙倍資料傳輸率同步隨機存取記憶體 (這名字真是越來越長了),與前代最明顯的差異依然是預取資料量的提升與傳輸架構上的改變,DDR3 SDRAM 的預取資料量再次翻倍為 8n,因此 DDR3 SDRAM 的 I/O 匯流排時脈又將是 DDR2 SDRAM 的兩倍。

至於架構方面主要的不同則是出現在記憶體控制器與記憶體模組之間的傳遞命令、位置、時脈或控制訊號方式上,以往的 DDR2 與 DDR 記憶體是使用「T 型拓樸」的方式進行,也就是記憶體控制器連結到記憶體模組之後再開枝散葉連到各個記憶體顆粒晶片上,而到了 DDR3 則改用「Fly-by」的架構,記憶體模組與記憶體控制器之間成為點對點 (此處是指只有單一 Rank 的情形,若為多 Rank 則仍為一對多,但以 Rank 為單位) 的架構 (這麼做的目的基本上與 NUMA 架構類似,為了減輕主幹匯流排的負擔),不過 DDR3 這種架構的特色理所當然就是不同位置的記憶體顆粒的延遲時間會不一致,距離主幹越遠的晶片將會有較大的延遲。

(上圖取自 www.bit-tech.net)

除了預取量的提升與架構的改變之外,DDR3 絕大多數的改進幾乎都跟省電有關 (其實跟處理器有點像啦,提升性能遇到瓶頸之後就轉彎去發展節能了),例如專門用於重設 (Reset) 訊號的針腳,可以讓記憶體在接收到重設命令時暫時停止所有操作並轉為最為省電的狀態,鎖向環電路、訊號收發電路與時脈產生器都會隨之暫停運作以節省電力。

另一項新功能則被稱為 SRT (Self-Refresh Temperature),可以讓記憶體根據實際對溫度進行偵測來最佳化記憶體顆粒晶片的溫控、時脈與電源管理 (透過自動調整重新充電的頻率來實現),並且支援對 Bank 的局部進行重新整理的功能 (PASR, Partial Array Self-Refresh) 也可以提高對記憶體顆粒晶片上的 Bank 進行寫入操作時的能源效率。

值得注意的是,在 2013 年附近開始低電壓版本的 DDR3L (電壓為 1.35 V) 被運用在不少系統上,儘管在說明上有不少文件說這兩種規則彼此互相相容,但實際上在某些較晚期的 DDR3L 主機板上是無法使用 DDR3 記憶體進行開機的,也強烈不建議同時混用這兩種記憶體,特別是基於 Haswell、Broadwell、Skylake 平台的系統,Intel 官方已經提出警告在這些系統上 (尤其是 Skylake) 使用 DDR3 記憶體可能會導致處理器內的整合記憶體控制器 (IMC) 損毀,請使用 DDR3L 記憶體 (不過如果你打算配 Skylake 平台的話,應該會選擇搭配 DDR4 記憶體吧?所以這個問題也不算很大)。

| 規格 | 制式 | 運作時脈 | 每秒資料傳輸率 |

| DDR3-800 (少見) | DDR3 | 100 MHz | 6400 MB/s |

| DDR3-1066 | DDR3 | 133 MHz | 8533 MB/s |

| DDR3-1333 (主流) | DDR3 | 166 MHz | 10.4 GB/s |

| DDR3-1600 (主流) | DDR3 | 200 MHz | 12.5 GB/s |

| DDR3-1866 | DDR3 | 233 MHz | 14.6 GB/s |

| DDR3-2133 (少見) | DDR3 | 266 MHz | 16.7 GB/s |

| DDR3-2400 (規格外) | DDR3 | 300 MHz | 18.8 GB/s |

DDR4 SDRAM

活躍年代:2014 年至今

針腳配置:288 針

封裝方式:BGA

工作電壓:1.2 V

單條模組最大容量:16 GB (UDIMM)、32 GB (RDIMM) 未來預估可以做到 128 GB

單一顆粒晶片 Bank 數量:8 (組成兩個 Bank Group) 或 16 (組成四個 Bank Group)

DDR4 SDRAM 是目前最新的雙倍資料傳輸率同步隨機存取記憶體規格,從 2014 下半年的 Intel Haswell-E/EP/EX 平台開始採用,並在 2015 年 Skylake 平台推出時正式進軍消費性個人電腦市場,而 2016 年正是 DDR4 SDRAM 記憶體開始大幅降價與大量普及的一年 (現在 DDR4 SDRAM 的價格幾乎跟 DDR3 SDRAM 一樣,甚至更低)。

DDR4 SDRAM 與前面幾代 DDR SDRAM 記憶體不同的地方是在此代中預取機制並沒有再次提升容量,仍然維持在 DDR3 SDRAM 使用的 8n 預取設計,據說是因為若要再次翻倍到 16n,會導致線路複雜度、製造的困難度與製造成本大幅提高所以才沒有選擇繼續提升預取資料量,但這時候就會產生一個很大的疑問了,以往的 DDR SDRAM 換代帶來的頻寬大幅飆升幾乎都來自於預取量的翻倍,那 DDR4 呢?該不會性能比起 DDR3 完全沒長進吧?

當然這個問題的答案我們都知道一定是否定的,雖然近年來電腦的發展進入明顯的停滯期,幾乎沒有突破性的技術與讓人驚豔的性能倍數提升出現,但廠商還是不至於無良拿完全沒改進卻與前代不相容的新產品來騙錢的,DDR4 當然還是有一定程度的改進的。

首先看到預取的部分,雖然預取的資料量仍然是 8n 沒有提升,但這次 DDR4 SDRAM 把腦筋動到記憶體顆粒晶片中的 Bank 上了,將 Bank 區分成數個不同的群組 (可能是二個或四個),每個 Bank Group 都像以前一樣可以進行 8n 的預取,而且可以在同一個時脈週期中同步進行資料存取操作 (類似多工的概念),這就是 DDR4 在記憶體顆粒晶片中提升性能的作法。

除此之外 DDR4 SDRAM 在記憶體拓樸的部分沿用了 DDR3 SDRAM 的 Fly-by 做法,至於匯流排的結構則在 DDR4 SDRAM 從以往的多重分支匯流排 (簡單來說這樣的方式可以比喻為每個記憶體通道有一條通往記憶體控制器的大型高速公路,但同一通道內的多個記憶體模組則需要共用這條高速公路) 變更為點對點的型式 (每個記憶體模組都有自己一條專用的快速道路直通記憶體控制器,儘管單條頻寬變窄,但卻不必共享與互等)。

至於確保資料完整性的技術,DDR4 SDRAM 在 ECC Registered 記憶體上加入了 Parity 檢查與資料匯流排 (寫入) 支援 CRC 校驗的功能,但這些特性在個人電腦使用的 Non-ECC Unbuffered 記憶體上則無法看到,其他一些比較細節的部分則是跟省電有關的技術,在此就省略不談了。

最後關於 DDR4 SDRAM 我想提的是外觀上的變化,注意到模組底下的金屬觸點的形狀怪怪的了嗎?並不是瑕疵品哦,其實這是 DDR4 SDRAM 的標準規定,目的是讓安裝或拆除記憶體的時候接觸面的摩擦力能夠減小,避免過去偶爾會發生因為施力不當使得記憶體沒有完全插入插槽中或是難以拔出的問題發生。

| 規格 | 制式 | 運作時脈 | 每秒資料傳輸率 |

| DDR4-1600 (少見) | DDR4 | 200 MHz | 12.5 GB/s |

| DDR4-1866 | DDR4 | 233 MHz | 14.6 GB/s |

| DDR4-2133 (主流) | DDR4 | 266 MHz | 16.7 GB/s |

| DDR4-2400 | DDR4 | 300 MHz | 18.8 GB/s |

| DDR4-2666 (規格外) | DDR4 | 333 MHz | 20.8 GB/s |

| DDR4-3200 (規格外) | DDR4 | 400 MHz | 25.0 GB/s |

歷代電腦用 SDRAM 橫向對比

看完這五代電腦用 SDRAM 的簡單介紹之後,接下來就是把這幾代的規格一次列出來做橫向比對,作為本節的收尾囉 (是的沒錯,篇幅又爆掉了)。

| 記憶體制式 | SDR | DDR | DDR2 | DDR3 | DDR4 |

| 發佈年代 | 1996 | 2001 | 2004 | 2007 | 2014 |

| 支援腳位 | 168 針 | 184 針 | 240 針 | 240 針 | 288 針 |

| 通道寬度 | 64-bit | 64-bit | 64-bit | 64-bit | 64-bit |

| JEDEC 時脈下限 (MHz) | 66 | 100 | 100 | 100 | 200 |

| JEDEC 時脈上限 (MHz) | 133 | 200 | 266 | 266 | 300 |

| JEDEC 最低理論傳輸率 | 528 MB/s | 1600 MB/s | 3200 MB/s | 6400 MB/s | 12.5 GB/s |

| JEDEC 最高理論傳輸率 | 1064 MB/s | 3200 MB/s | 8533 MB/s | 16.7 GB/s | 18.8 GB/s |

| 單條最大容量 (UDIMM) | 1 GB | 1 GB | 4 GB | 8 GB | 16 GB |

| 單條最大容量 (RDIMM) | 2 GB | 2 GB | 8 GB | 16 GB | 32 GB |

| Bank 數量 | 2、4 | 4 | 4 或 8 | 8 | 8 或 16 |

| 記憶體拓樸 | T 型 | T 型 | T 型 | Fly-by | Fly-by |

| 記憶體連結形式 | 多重分支 | 多重分支 | 多重分支 | 多重分支 | 點對點 |

| Bank Group | 0 | 0 | 0 | 0 | 2 或 4 |

| 工作電壓 | 3.3 V | 2.5 V | 1.8 V | 1.5 V | 1.2 V |

| 預取資料量 | 1n | 2n | 4n | 8n | 8n |

| 顆粒晶片封裝方式 | TSOP | TSOP/BGA | BGA | BGA | BGA |

| 容量密度 (最小) | 64 Mb | 128 Mb | 256 Mb | 512 Mb | 2 Gb |

| 容量密度 (最大) | 512 Mb | 1 Gb | 4 Gb | 8 Gb | 16 Gb |

| 傳輸介面 | LVTTL | SSTL_2 | SSTL_18 | SSTL_15 | POD_12 |