由於篇幅過長,因此站長在完稿之後決定將 Intel Core 架構的前世今生分成兩篇,這篇是下篇 (Intel Core 架構的逆襲),主要談 Core 架構本身。

其實站長等著要寫這篇等很久了,2006 年應該是近代 CPU 發展史上最戲劇化的一年,同時也是奠定未來好幾年 (至今仍是) 個人電腦世界基礎的一年。

從 Intel Core 2 系列開始的 Intel CPU,在規格參數上高低落差很大 (因為共用架構之後型號與產品線差異來自於規格數字的直接調整),因此從本篇開始站長將不再放上先前幾篇文章有的處理器參數介紹。

Table of Contents

Intel Core Microarchitecture

站長要再次強調 2006 這個年份在個人電腦發展史上的重要意義,2006 年同時是 Intel 最慘的一年,卻也是奠基後來從 Nehalem、Sandy Bridge、Ivy Bridge、Haswell、Broadwell、Skylake 甚至未來可見的所有 Intel x86 處理器架構基礎的 Intel Core 架構誕生的一年,說是帝國復興、絕地反攻其實一點也不為過。

架構回歸統一局面

由於相較於 Netburst 架構的失敗而言,Pentium M 與 Yonah 架構可說是獲得了巨大的成功,因此 2006 年下半推出的 Core 架構再次將行動平台與桌面、伺服器平台的 x86 處理器架構統一,整體而言 Core 架構的特性仍然比較接近 Pentium M 與更早期的 P6 架構,因此一般而言我們會認為 Pentium M 就是 Core 架構的前身 (儘管 Intel 官方一再強調 Core 架構是從零打造起的,且融合了 Netburst 與 Pentium M 的架構,不過基本上只是為了給 Netburst 一個比較好的下台階而已)。

第一款基於 Core 架構的處理器是 Core 2 Duo,相較於前做 Yonah 而言比較明顯的差異是 L2 快取大小的大幅提升與納入早已出現在晚期 Netburst 架構產品中出現的 EM64T。

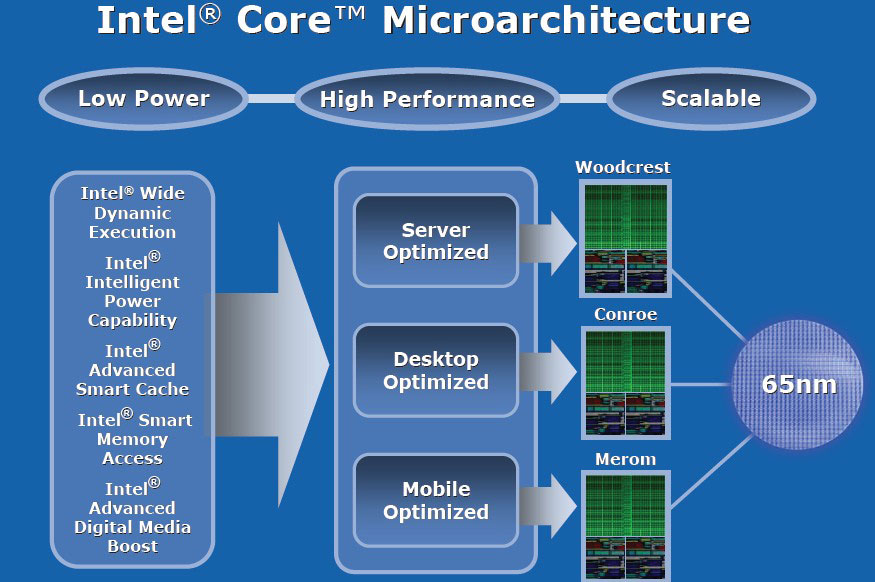

Intel Core 架構主要有三大面向的特性,分別是低耗電、高性能與可擴展性,其中最容易說明且至今仍然適用的是可擴展性這項,因此站長打算先說明。

可擴展的架構設計

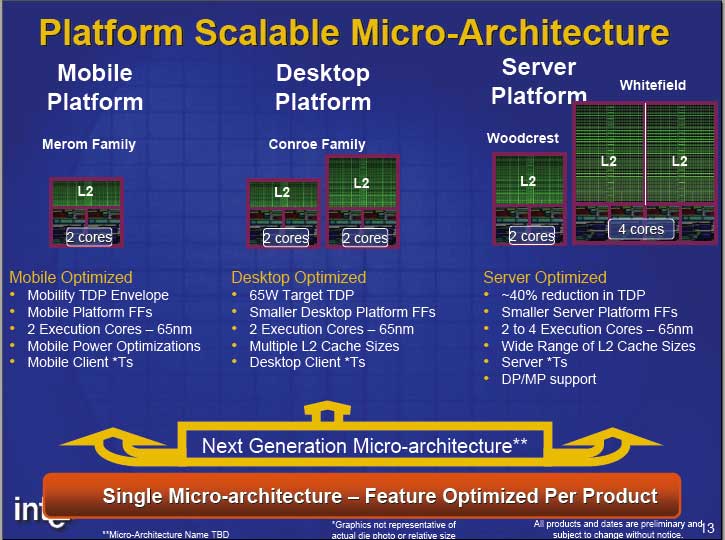

可擴展性可分為兩個層次,第一個層次是架構可以適用的範圍有多廣 (Platform Scalable),以 Core 架構而言,伺服器級別的 Woodcrest、個人電腦使用的 Conroe、筆記型電腦使用的 Merom 都是從同樣的 Core 架構與同樣的 65 奈米製造工藝分化出來的。

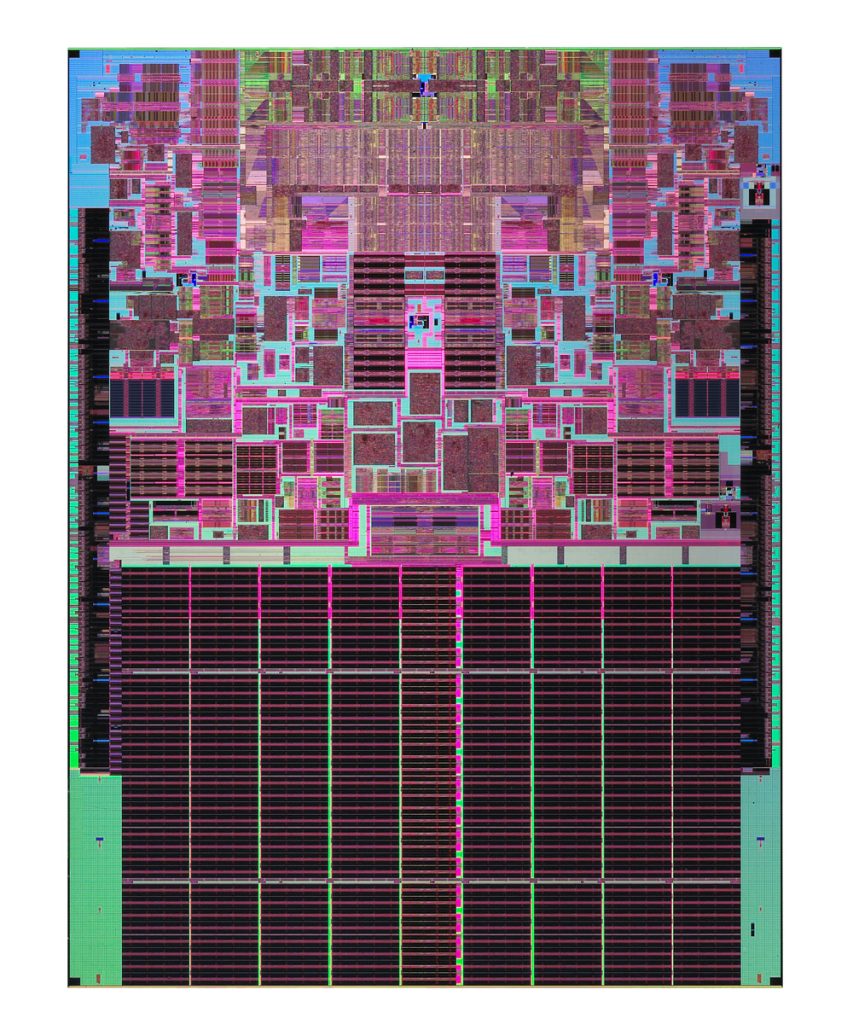

↑ Intel Xeon (基於 Core 架構,代號為 Woodcrest) 的 die shot

Intel 開發的時候是先設計出共同的「架構」之後才去分化出不同用途與級別的型號,有需要時 Intel 可以很容易地透過「複製」的方式延展處理器的結構,製造出四核心以上同架構處理器。

第二個層次則是處理器內部結構的模組化設計 (Modular Design),這個特性要等到再下一代的 Nehalem 架構才見得到,因此站長留待屆時再說明。

朝向高效率的設計觀點

如同前面所說的,以往 Netburst 架構強調整體性能的提升,因此選擇追求拉高時脈,儘管因此造成分支預測命中率下降、IPC 性能低落等問題,但在時脈的瘋漲之下總體的性能仍然是提高的,因此在當時被認為是「好的發展方向」,處理器改良的目的在於極盡所能地提高性能,至於省電與發熱量的降低則不是主要考量。

然而這樣的設計方針在 Netburst 走到後期時已經被證實並不可行,因為散熱裝置無法無止盡的延伸下去來承受處理器發熱量的不斷增長,而且處理器發熱量增長的幅度到了後期已經遠遠超出性能的增加幅度,在無止盡的拉高時脈之後性能提升的幅度越來越少,甚至呈現負成長。

因此從 Pentium M 開始,到 Core 架構與現今的 Intel 處理器都朝向提高「效率」的方向前進,強調的是每單位耗能 (瓦) 能帶來的性能有多少,效率是能耗與性能的比值,因此除了提高性能很重要之外,降低能耗與發熱量也是重點。

Core 架構的新特性

Intel 在宣傳 Core 架構時主要強調這五個新特性:

- 寬頻動態執行技術 (Wide Dynamic Execution)

- 智慧型記憶體存取技術 (Smart Memory Access)

- 進階智慧型快取 (Advanced Smart Cache)

- 進階數位媒體增強技術 (Advanced Digital Media Boost)

- 智慧型電源管理功能 (Intellignet Power Capability)

不過既然是宣傳用的,其實這五大點沒辦法完整說明 Core 架構引入的新特性,所以站長還是拆開來說明。

寬頻動態執行技術 (Wide Dynamic Execution)

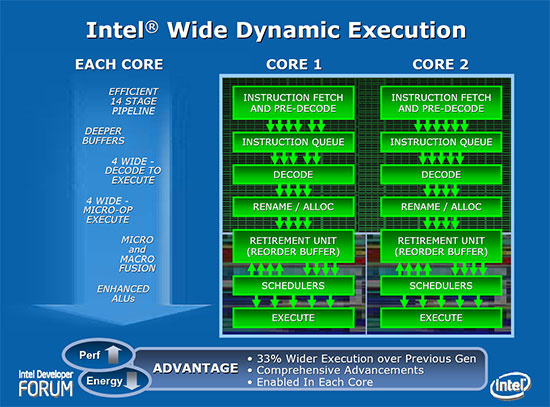

寬頻動態執行技術 (Wide Dynamic Execution) 其實包含了很多東西,例如接下來介紹的巨集融合技術、比 Pentium M 略多一些的 14 級管線設計 (還是不到 Prescott 誇張的 31 級管線的一半呢)、每個 cycle 可以處理四個指令 (如果有使用到巨集融合則可以是五個) 等,同時 Core 架構的 Simple Decoder 比以往多了一組,分支預測的頻寬比 Banias 多了 25%,同時也是 Netburst 的五倍。

巨集融合技術 (Macro-Fusion)

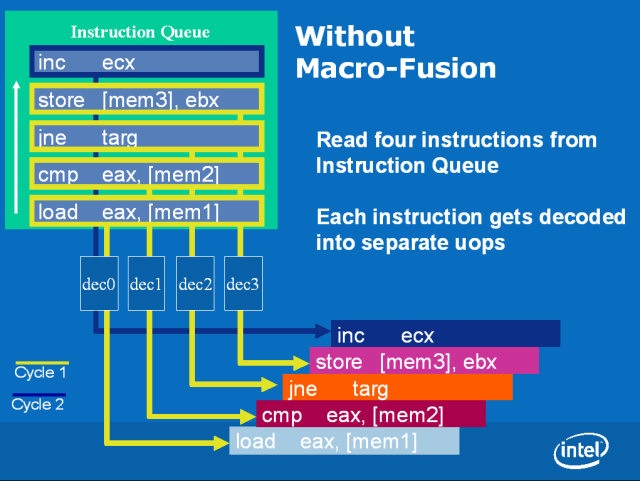

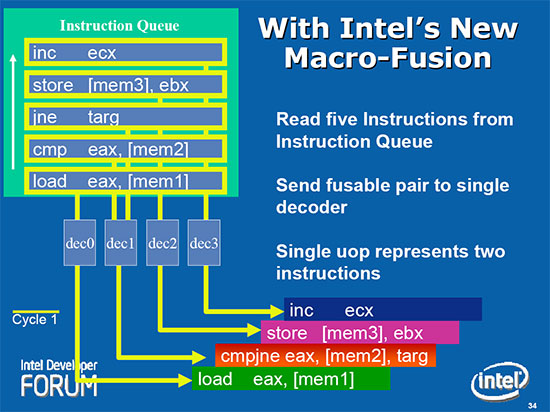

巨集融合是 Intel Core 架構中很重要的一個特性,主要的意思是在指令解碼的階段將特定種類 (不是隨便兩條指令都可以融合) 的兩條連續的 x86 指令合而為一,從而提升指令解碼與執行的效率,在此代 Core 架構中只能融合 32 位元指令,因此在 Core 2 系列上有時候可以觀察到 32 位元版本程式比 64 位元版本還要快 (除了巨集融合以外另一個原因是 EM64T 只能使用特定幾個專屬的暫存器)。

儘管巨集融合支援的指令種類相當有限,能融合的情況下也有很多條件要求 (例如必須連續、一個時脈周期內只能融合一組、被融合的第一條指令中必須至少用到一個暫存器等),但由於實務上符合條件的情況在編譯完成之後的程式中非常常見,因此對性能的提升是可見的 (而且不需要重新編譯就能享受到提升),之後歷代的 Core 處理器也幾乎都會對巨集融合這項功能進行強化,足見這項功能的重要性。

進階智慧型快取 (Advanced Smart Cache)

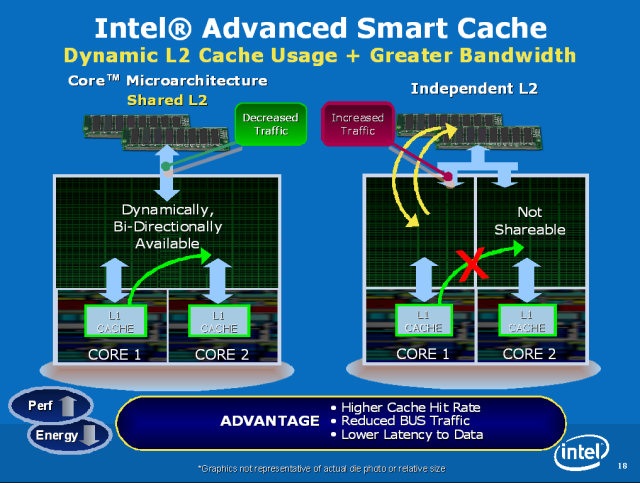

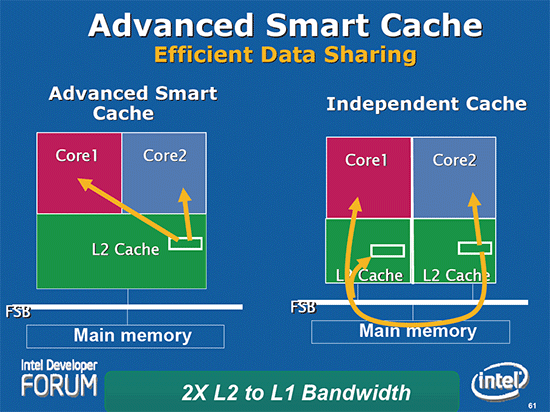

其實這項技術說穿了就是兩個核心共用一個大的 L2 快取,從而降低 L2 快取的失誤率 (miss rate),因為以前各自使用專屬 L2 快取的時候經常會發生 Core 1 需要的資料在 Core 2 的 L2 快取,或是反過來,而這種情況會導致 L2 快取失誤,以致於需要向較慢的記憶體重新取得資料,而且出現在錯誤位置的資料反而變成占用該核心所屬 L2 快取,連帶也讓另一個核心的 L2 快取失誤率拉高。

而且很多時候其實兩個核心的負載不會剛好平分,改成共用快取可以讓處理器動態分配,給負載較高或需要較多快取的核心更多資源 (不論是快取大小或頻寬)。

要注意的是,今日 Intel CPU 的 Smart Cache 其實是指 L3 共用快取 (以 Skylake 為例,L2 是每個核心各自專屬的),但在 Core 2 的時代指的則是 L2。

此外這項設計也給處理器核心之間一個互相溝通的管道,以往兩個處理器核心之間是沒有連結的,如此造成系統的前端匯流排負擔變得非常重 (一次只能接受一個核心使用,再加上一次只能處理一個方向,因此常常會發生排隊排到天荒地老的狀況),以 Core 2 需要 Core 1 所屬 L2 Cache 中的資料為例,得從 Core 2 走 FSB 到主機板北橋、記憶體繞一圈回到 Core 1 的 L2 Cache 才拿得到。

至於在省電方面的幫助則是處理器現在可以關閉暫時沒有用到的 L2 部分電路,或是關掉其中一個核心卻維持整個 L2 的運作,不像以前是以核心為單位,一次關得全關,有更高的彈性來達到更省電的效果。

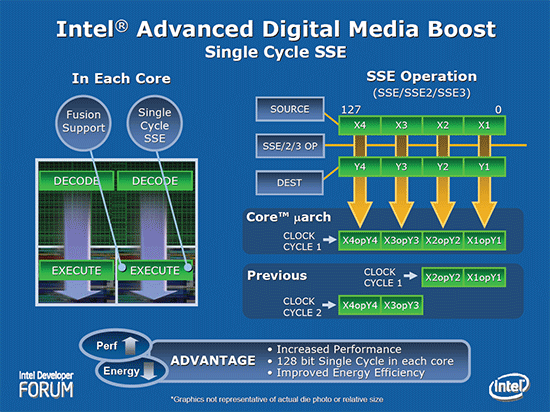

進階數位媒體增強技術 (Advanced Digital Media Boost)

以往受制於實際電路中只設計一組 64 位元的 SSE 運算電路,一個 128-bit 的 SSE 指令會需要兩個 cycle 才能完成,Core 架構中的乘法、加法、載入、儲存指令都能一次處理 128-bit 長的指令,所以又稱為 Single cycle SSE。

智慧型記憶體存取技術 (Smart Memory Access)

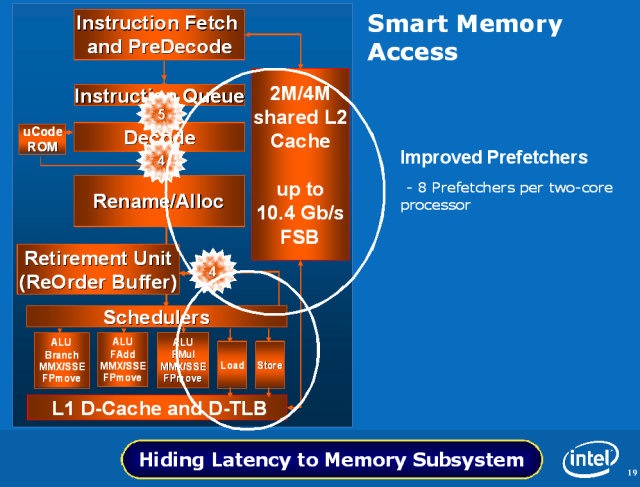

這部分比較難解釋,主要是關於 Core 架構降低資料存取延遲對系統性能影響的努力,例如用上 8-Way 的 L1 Cache、16-Way 的超大 L2 快取等,並放棄了過去 Netburst 架構設計的追蹤快取 (Trace Cache) 設計。

Core 架構中,每個核心有四組預取器 (Prefetcher),其中一組負責預取指令,一組負責預取 L2 快取,兩組負責記憶體預取,讓處理器有能力「學習」最佳的資料存取方式以降低延遲。

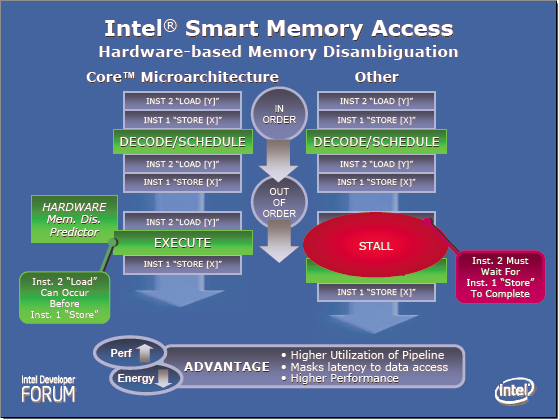

另一項重要的功能稱為 Memory Disambiguation,透過硬體上實作電路來達到預測後續的指令是否會用到相同的記憶體位置,從而避免不必要的指令等待,能夠提升亂序執行的性能。

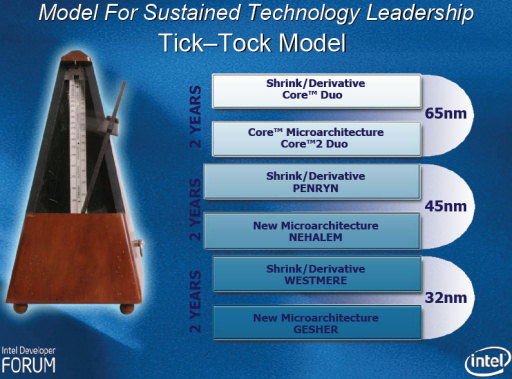

首次引入 Tick-Tock 戰略規劃

眾所皆知的 Tick-Tock 兩年一輪戰略規劃也是從 2006 年開始的,可以看到後續的 Nehalem、Westmere 都是早在當時就已經確定的規劃,至於最下面的 Gesher 後來則改名為 Sandy Bridge。

第二代 Intel Core Microarchitecture (Penryn)

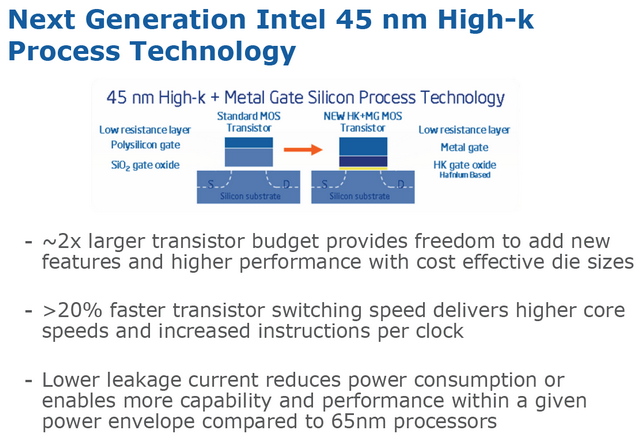

Intel 在 2008 年依照 Tick-Tock 戰略規劃的預期,推出了稱為 Penryn 的新版架構,Penryn 基本上可以認為是 Core 架構的製程升級版,導入新的 45 奈米製造工藝與 High-K 金屬閘極技術。

隨著製程的不斷縮小,漏電流對半導體製成品的影響越來越明顯,有越來越高比例的能耗其實是被漏電流「浪費掉」的,因此必然需要做額外的努力來降低漏電流的產生,這就是 High-K 金屬閘極技術的目的,同時號稱能提高 20% 的電晶體切換速度,可以帶來更高的 CPI 與時脈。

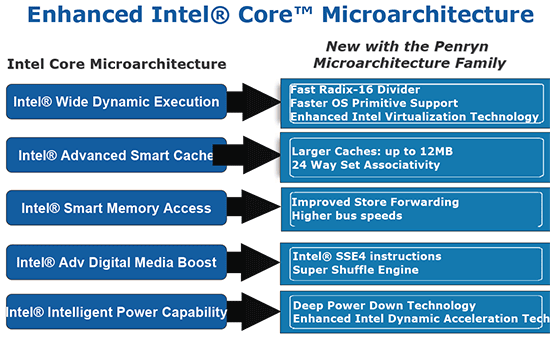

然而除了製程以外,Penryn 與 Core 在架構上還是有一些不同的,這些不同都是依據 Core 架構強調的五大特性進行更多的強化以求能榨出 Core 架構中潛藏的性能。

主要比較明顯的新特性是新加入的 SSE4.1 指令集、更快的前端匯流排 (FSB) 與更大的 L2 快取 (加大 50%)、速度更快的 Radix-16 除法器,除了這些之外,Intel 表示在虛擬化技術的性能上也有提升。

結語

我想 Intel 在 2006 年發生的事情可以說完美舉例了「危機就是轉機」、「有心栽花花不開,無心插柳柳成蔭」這兩句話吧,當年耗費如此多的功夫想發展「全新」的 Netburst 架構,覺得未來會非常順利的一路向前發展,最後才發現其實當初認為沒有辦法再走下去而被棄置一旁的 P6 架構才是公司真正的未來,從 P6 架構改良而來的 Core 架構奠下的基礎幾乎讓往後十年 (至今依然如此) 的 Intel 幾乎立於不敗之地。

「電腦達人養成計畫 2-12:近代中期 CPU 發展史 (一) Intel Core 的前世」<< PREV

NEXT >>【COMING SOON】

![[下載] VMware ESXi 6.0 正式版 (GA)](https://isite.tw/wp-content/uploads/2015/03/vmware-partner-link-bg-w-logo-360x180.png)

![[CES 2019 速報] AMD 預覽下一代 “Zen 2” 處理器,可望成為本屆 CES 最大看點](https://isite.tw/wp-content/uploads/2019/01/AED8012-360x180.jpg)

![[教學] 使用 XperiFirm 製作 Xperia 手機原廠軟體 FTF 安裝包](https://isite.tw/wp-content/uploads/2016/04/XFX0001-360x180.png)

![[ 突發 ] Mega 創辦人呼籲大眾盡速備份 Mega 上的資料?! (附官方澄清)](https://isite.tw/wp-content/uploads/2016/04/AMU8563-360x180.jpg)

![[ WP 外掛 ] Duplicate Post 輕鬆一鍵將文章當成範本複製](https://isite.tw/wp-content/uploads/2016/04/wp-logo-360x180.png)