Table of Contents

核心架構上的改進 (真的不多)

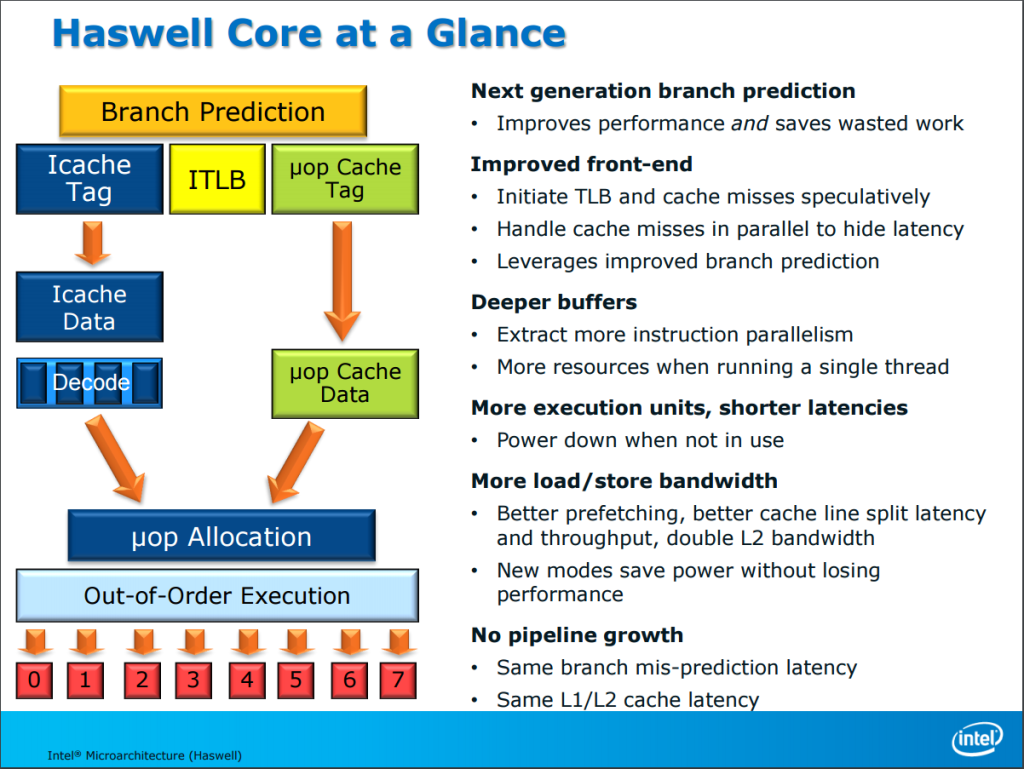

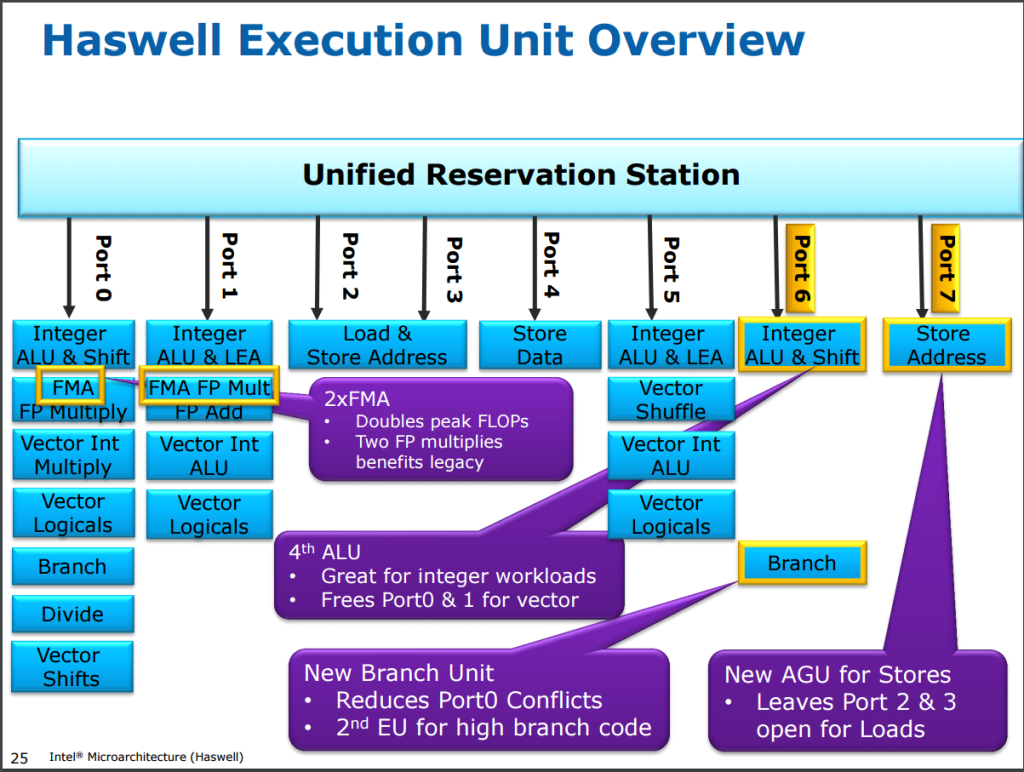

Intel 在談及 Haswell 核心架構改進時,顯得比過去 IVB、SNB 都還要籠統許多,架構的部分與 Ivy Bridge 基本上是相同的,但再次針對分支預測進行提升,並優化了前端的性能 (更大的亂序執行結構、指令讀取頻寬,除此之外指令發射埠也從六個增加到八個),L2 快取的 TLB 也有增大,但是運算管線的「結構」就幾乎沒有任何改變了 (當然強化也是有啦,畢竟加了一個「很大組」的新指令集呢)。

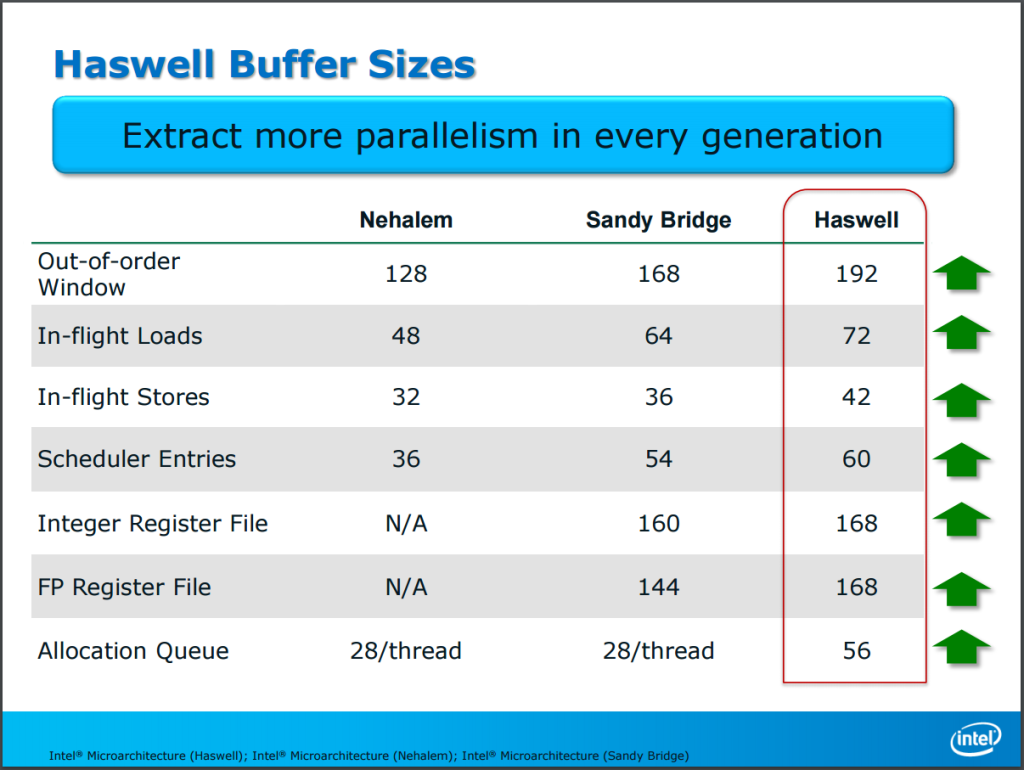

除此之外 Haswell 的各類緩衝區基本上大小都有成長 (說起來在 SNB 時代 Intel 是沒有特別提這個的,或許是 HSW 真的沒有太多新特色吧?)

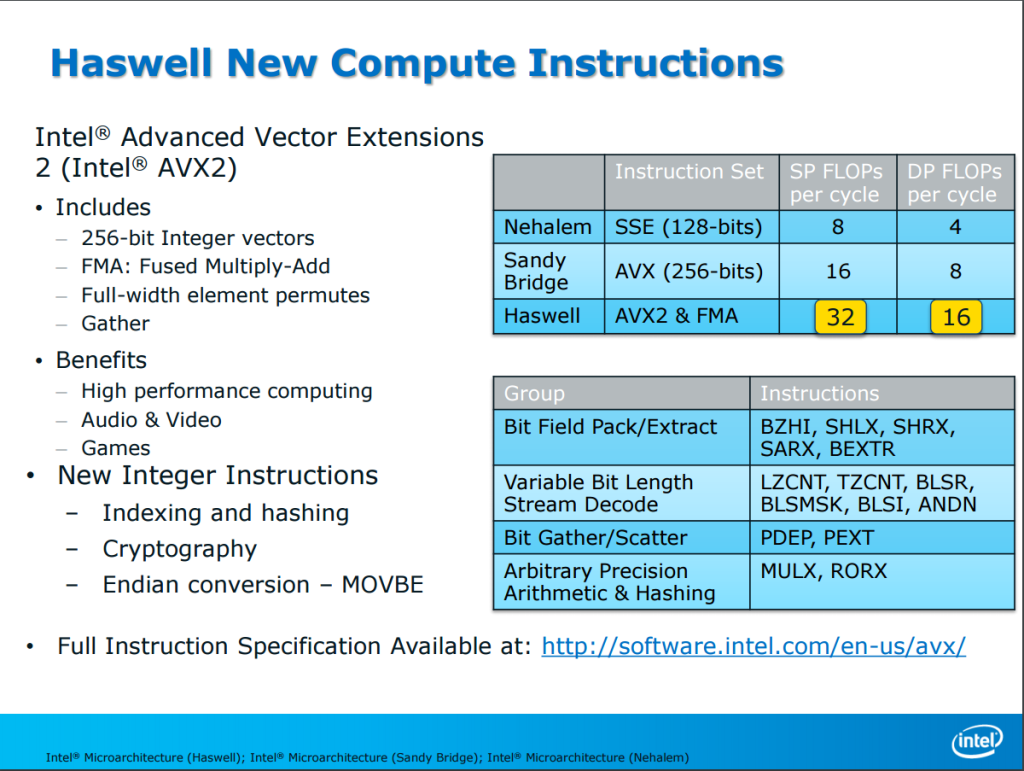

AVX2 指令集

AVX2 指令集算是 Haswell 架構最主要的新特色之一,發佈之前也曾經被稱為 HSW-NI (Haswell New Instruction Set),透過新增 60 條 256-bit 浮點 SIMD 指令與增加兩組 FMA3 融合乘加單元 (Fused Multiply-Add,負責狀似 ±(a×b)±c 的計算操作,值得注意的是不同於 AMD 主推的 FMA4 採用四運算子,Intel 陣營的 FMA3 是三運算子的) 來讓每時脈週期處理器核心可以處理的 FLOPs (浮點數操作) 提高到兩倍 (SNB 時期是 16 個單精度、8 個雙精度,HSW 直接拉高到 32 個單精度、16 個雙精度),並且將 AVX 拓展到整數向量上,能夠支援 256-bit 的整數 SIMD (以往只支援到 128-bit),適用範圍變得更廣。

下圖顯示的就是 Haswell 的運算單元架構圖,可以看到新增的兩個指令發射埠 (Port 6 用於分攤原本 Port 1 與 Port 2 的工作、Port 7 用於分攤原本 Port 2 與 Port 3 儲存位置的任務) 以及新增的兩組融合乘加單元。

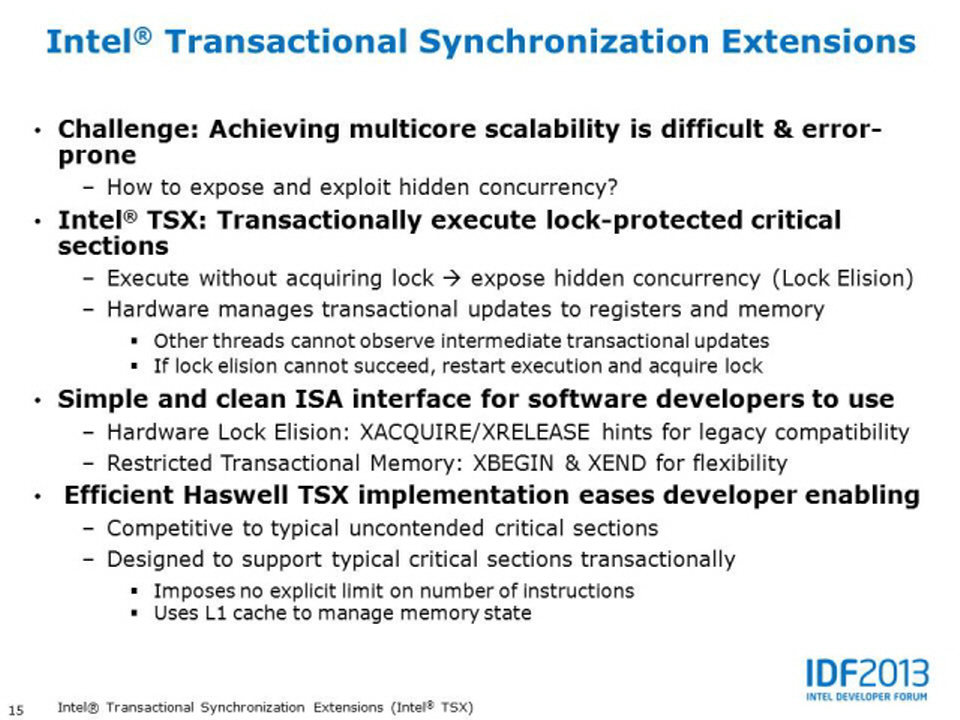

悲劇的 TSX-NI 指令集

TSX-NI 指令集幾乎可以說從頭到尾就是個悲劇,首先因為名字太難翻譯所以很少人記得 (事務性同步擴展指令集)、做的事情很難解釋 (只能說他跟解決多執行緒、多核心之間的鎖定、同步問題有關,透過硬體層面對這個問題進行改善,讓軟體工程師能夠更容易解決或是降低這個問題帶來的影響)、一般人沒有感覺 (因為主要是跟軟體工程師比較有關) 所以根本沒多少人認識它。

沒人認識與記得已經很悲劇了,但更悲劇的是這個指令集在 Haswell 架構處理器當中是有缺陷的,甚至 Broadwell 也無法倖免,Intel 官方透過更新微碼禁用 TSX-NI 指令集來解決,結果最後有一部分人記得這東西的原因居然反而是因為 Intel 在 Haswell 中做壞了,夠悲劇吧。 XD

其實我個人的感覺是 Intel 官方並不是真心想推這個指令集,因為這指令集需要依賴軟體支援的成分很大,但在 Haswell 的 K 版不鎖頻處理器與高端 HEDT 市場的 Haswell-E 都是全線不支援的,面向伺服器的 Haswell-EP 也有一堆型號不支援,後來 Intel 也很少再提起這個指令集,當能使用的人數少,它成為軟體工程師採用方案的機率就很低,因為通常而言開發軟體當然是希望越多人能夠使用越好。

![[下載] VMware ESXi 6.0 正式版 (GA)](https://isite.tw/wp-content/uploads/2015/03/vmware-partner-link-bg-w-logo-360x180.png)

![[CES 2019 速報] AMD 預覽下一代 “Zen 2” 處理器,可望成為本屆 CES 最大看點](https://isite.tw/wp-content/uploads/2019/01/AED8012-360x180.jpg)

![[教學] 使用 XperiFirm 製作 Xperia 手機原廠軟體 FTF 安裝包](https://isite.tw/wp-content/uploads/2016/04/XFX0001-360x180.png)

![[ 突發 ] Mega 創辦人呼籲大眾盡速備份 Mega 上的資料?! (附官方澄清)](https://isite.tw/wp-content/uploads/2016/04/AMU8563-360x180.jpg)

![[ WP 外掛 ] Duplicate Post 輕鬆一鍵將文章當成範本複製](https://isite.tw/wp-content/uploads/2016/04/wp-logo-360x180.png)