Table of Contents

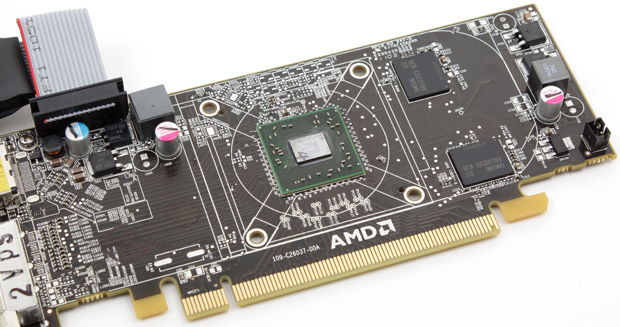

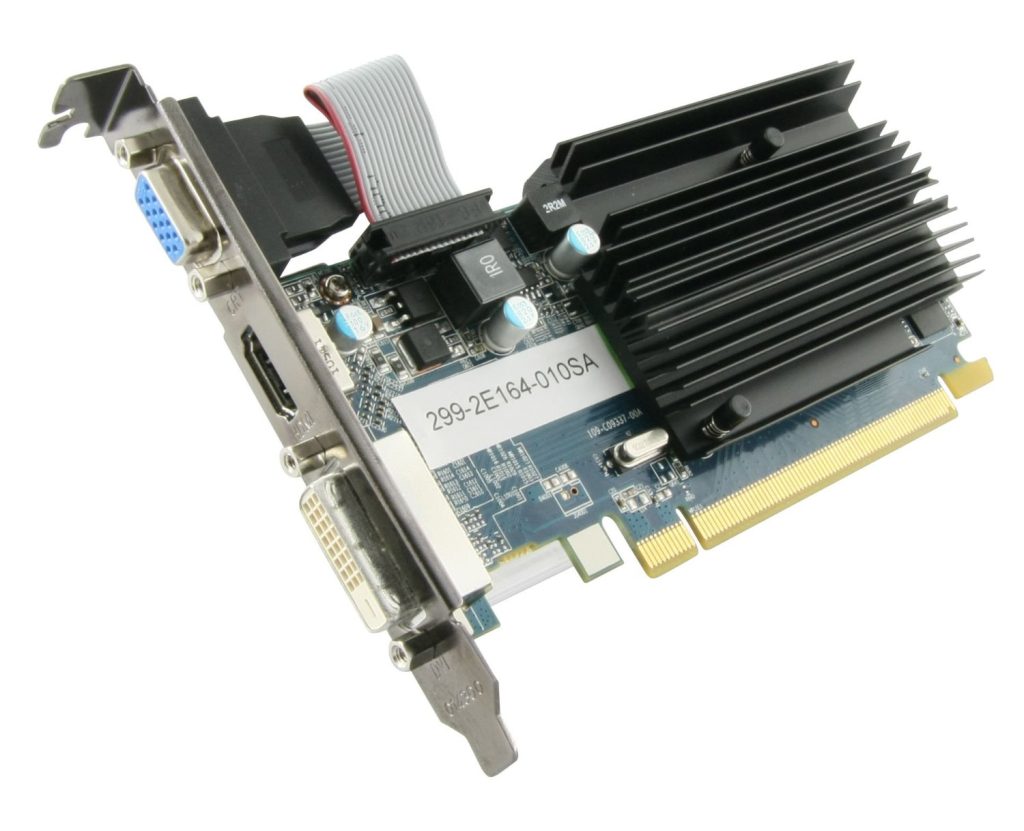

Caicos 核心

接下來介紹的則是北方群島家族當中規格最差的一款核心-Caicos 核心,實際上 Caicos 的定位還略高於真正的入門款 Cedar,相較於 Cedar 來說 Caicos 的 SC 數量多了一倍,其他參數則維持不變。

基於 Caicos 核心的型號一開始只有 HD 6450 一款 (625/800 MHz 或 750/900 MHz + DDR3),但之後的 HD 7000 系列與 HD 8000 系列都有拿 Caicos 核心再來更名重出做為入門產品之用,例如 HD 7470 (625/800 MHz + GDDR3 或 775/900 MHz + GDDR5)、HD 7450 (625/533 MHz 或 750/800 MHz + GDDR3) 與後來的 HD 8490 (875/900 MHz + GDDR5)、HD 8470 (750/800 MHz + GDDR5)、HD 8450 (625/533 MHz + DDR3),不過這幾款都只針對 OEM 市場推出。

Caicos 核心應該是所有 Terascale 2 架構衍生產品當中壽命最長的一款,後來的 R5 200 系列當中有多達四款產品都是使用 Caicos 核心,分別是 R5 220、R5 230、R5 235、R5 235X,其中除了最低階的 R5 220 採用閹割一半的 Caicos 核心 (因此參數與 Cedar 幾乎一樣) 之外均為完整核心,並均搭配 DDR3 記憶體,不過其中只有 R5 230 有零售版本。

AMD Terascale 3

- 推出日期:2010 年 12 月 (Cayman)

- 所屬系列編成:Radeon HD 6000 系列

- API 支援:DirectX 11.0、OpenGL 4.4、OpenCL 1.2

- Shader Model 支援:SM 5.0

剛剛提過 Barts 相對於 Cypress 來說在規模上倒退導致實際性能並沒有辦法如同過去幾次改朝換代一般壓倒性的勝過前代產品,因此實際上 AMD 在 Barts 之上還是有推出產品的,而且實質上是大核心 (其實發展到這裡 AMD 的小核心戰略已經有點走偏了,畢竟這回的旗艦產品其實核心大小已經遠遠超過 Cypress,已經幾乎快要逼近慘烈的 R600 了,因此小核心戰略走到這裡其實已經只是安慰自己在大核心性能上追不上 NVIDIA 的藉口罷了)。

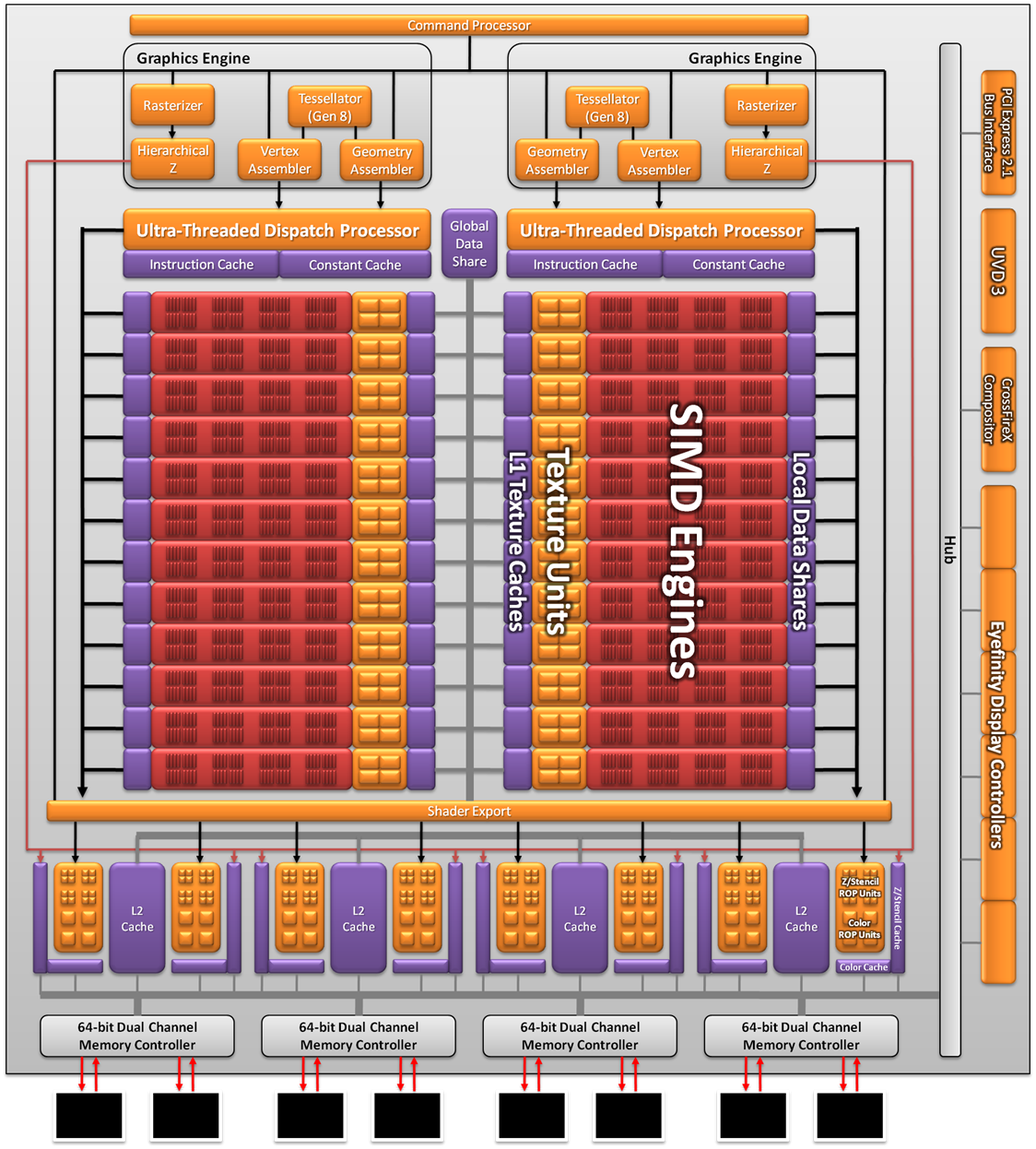

使用 Terascale 3 架構的產品很少,在 AMD 顯示卡當中只有 HD 6000 這一世代的旗艦產品有用到,除此之外則是出現在 APU 上。而實際上的差別呢,基本上與 Terascale 2 架構相比,Terascale 3 架構只在兩個部分有比較明顯的改變。

新的 SIMD 架構設計 (VLIW 4)

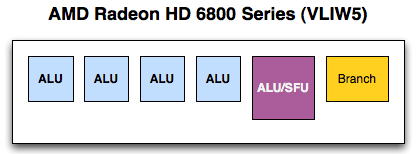

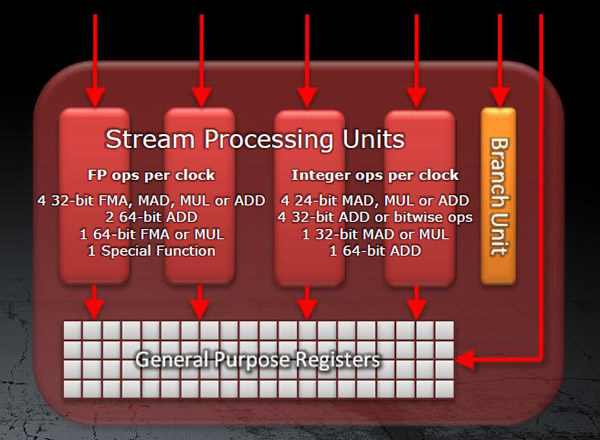

這是 Terascale 3 相較於先前架構當中最大、最明顯的不同,我們前面談過很多次 Terascale 1 與 Terascale 2 架構都是在 Very-Long Instruction Word (VLIW) 5 架構下設計出來的產物,不同於 NVIDIA 採用的小型 CUDA Core 設計 (每個 CUDA Core 實際上就是單獨的 ALU),AMD 的做法是在每個 SP 當中內建五個運算單元 (實際上是由四個 ALU 與一個 ALU 與特殊功能合併單元、分支單元三類組成)。

這樣的設計所造成的缺點大致上我在前面的篇章當中也都談過了 (像是高度依賴驅動程式優化、在通用運算方面效率不彰等,這些缺點在通用運算越來越重要、程式越來越複雜、AMD 認清自家驅動程式撰寫能力不強的事實之後更顯突出),除此之外還加上 SIMD Engine 數量的提升基本上也已經差不多面臨極限,因此要進一步追求性能提升 AMD 只能開始思考架構上的改變,於是新的 VLIW 4 架構就因此誕生了 (說起來這是從 R600 以來 AMD 第一次真的針對 GPU 架構內部有大幅度的調整)。

VLIW 4 與 VLIW 5 最明顯的不同主要出現在兩個地方,首先是組成 SP 的 SPU 數量從原來的 4+1 調整為單純的四組 (所以每組 SIMD Engine 包含的 SC 數量從 80 下降為 64 個了),除此之外則是以往被獨立出來的 SFU (也就是第五號 SPU) 的設計被取消了,現在剩下來的四組 ALU 都有著相同的處理能力 (只要抓其中任三組 ALU 就可以充當 SPU 用了),因此能夠更彈性的被隨時調用,這意味著資源的利用率提高了,而且實際上不僅僅是小幅的提高,在新設計當中利用率提高的幅度 (一方面也是對驅動程式依賴度下降帶來的好處) 能夠輕易彌補少掉一組 ALU 的不足,而且甚至還可以提供比起前代來說更高的性能,同時還因為效率提高,因此「每平方公分面積所能帶來的性能」也就隨之增加了。

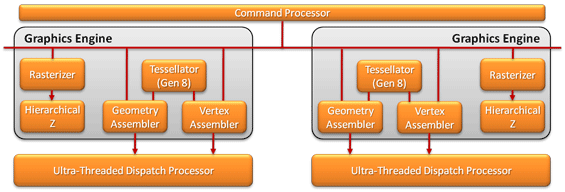

真正的雙 Ultra-Threaded Dispatch Processor

還記得剛剛在談 Barts 的時候我說 Barts 架構圖當中的 Ultra-Threaded Dispatch Processor 只是障眼法,實際上仍然只有一組,只是內部的「部分零件變成兩組」吧,在 Terascale 3 架構當中真的是如假包換的雙 Ultra-Threaded Dispatch Processor 設計了。

![[下載] VMware ESXi 6.0 正式版 (GA)](https://isite.tw/wp-content/uploads/2015/03/vmware-partner-link-bg-w-logo-360x180.png)

![[CES 2019 速報] AMD 預覽下一代 “Zen 2” 處理器,可望成為本屆 CES 最大看點](https://isite.tw/wp-content/uploads/2019/01/AED8012-360x180.jpg)

![[教學] 使用 XperiFirm 製作 Xperia 手機原廠軟體 FTF 安裝包](https://isite.tw/wp-content/uploads/2016/04/XFX0001-360x180.png)

![[ 突發 ] Mega 創辦人呼籲大眾盡速備份 Mega 上的資料?! (附官方澄清)](https://isite.tw/wp-content/uploads/2016/04/AMU8563-360x180.jpg)

![[ WP 外掛 ] Duplicate Post 輕鬆一鍵將文章當成範本複製](https://isite.tw/wp-content/uploads/2016/04/wp-logo-360x180.png)